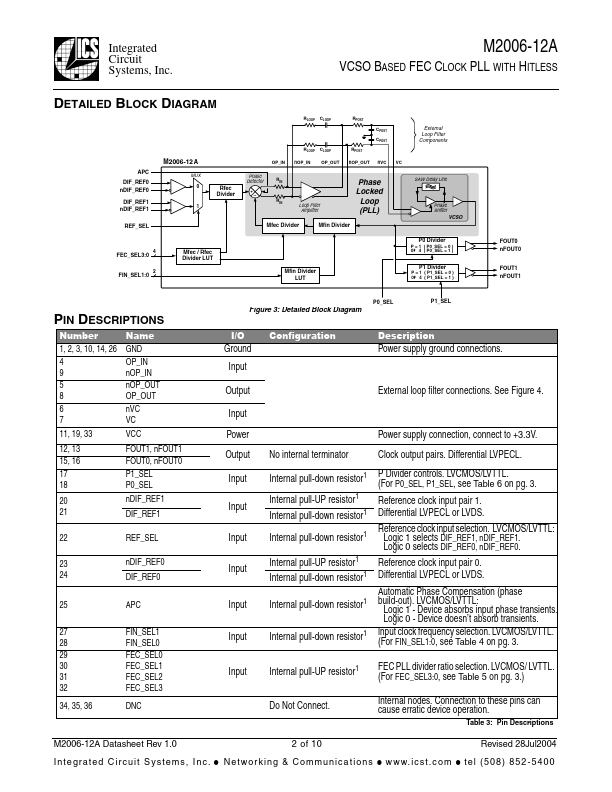

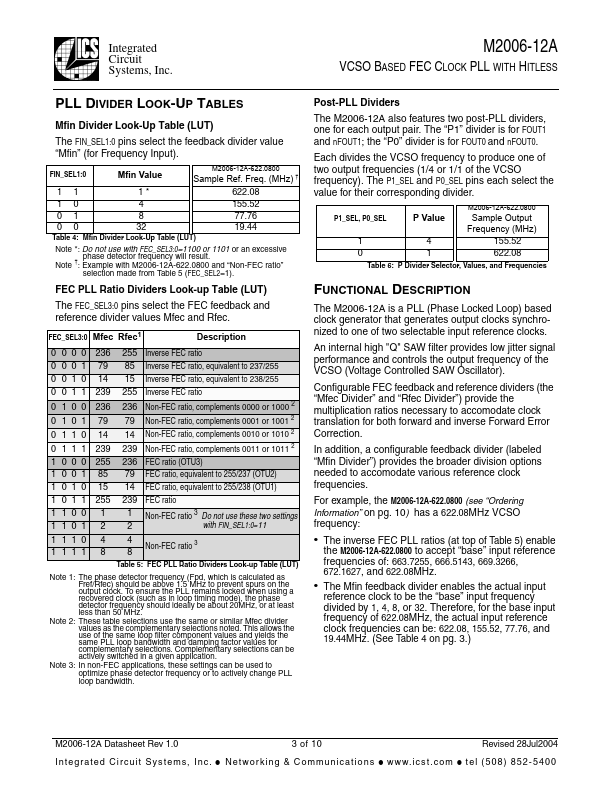

M2006-12A Datasheet Text

Integrated Circuit Systems, Inc.

Product Data Sheet

M2006-12A

VCSO BASED FEC CLOCK PLL WITH HITLESS SWITCHING

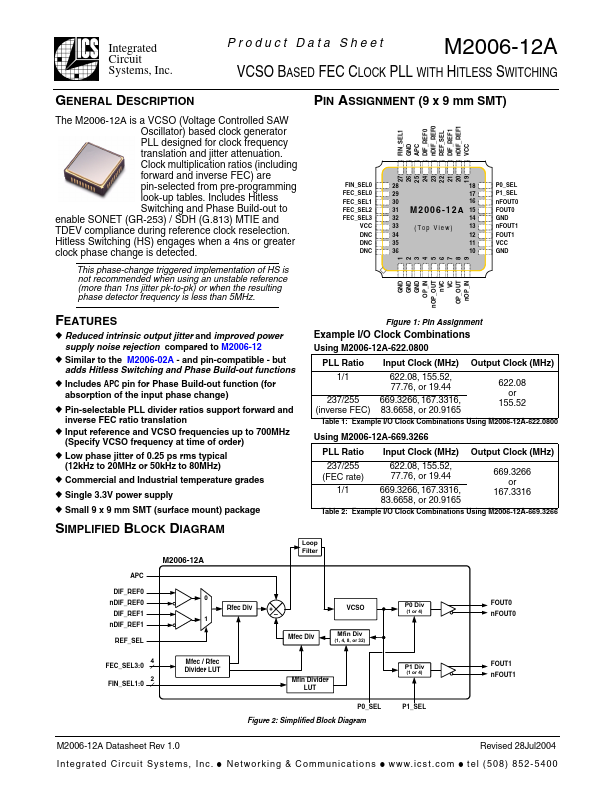

PIN ASSIGNMENT (9 x 9 mm SMT)

FIN_SEL1 GND APC DIF_REF0 nDIF_REF0 REF_SEL DIF_REF1 nDIF_REF1 VCC FIN_SEL0 FEC_SEL0 FEC_SEL1 FEC_SEL2 FEC_SEL3 VCC DNC DNC DNC 27 26 25 24 23 22 21 20 19

GENERAL DESCRIPTION

The M2006-12A is a VCSO (Voltage Controlled SAW Oscillator) based clock generator PLL designed for clock frequency translation and jitter attenuation. Clock multiplication ratios (including forward and inverse FEC) are pin-selected from pre-programming look-up tables. Includes Hitless Switching and Phase Build-out to enable SONET (GR-253) / SDH (G.813) MTIE and TDEV pliance during reference clock reselection. Hitless Switching (HS) engages when a 4ns or greater clock phase change is detected.

This phase-change triggered implementation of HS is not remended when using an unstable reference (more than 1ns jitter pk-to-pk) or when the resulting phase detector frequency is less than 5MHz.

28 29 30 31 32 33 34 35 36

M2006-12A

(Top View)

18 17 16 15 14 13 12 11 10

P0_SEL P1_SEL nFOUT0 FOUT0 GND nFOUT1 FOUT1 VCC GND

Features

- Reduced intrinsic output jitter and improved power supply noise rejection pared to M2006-12

- Similar to the M2006-02A

- and pin-patible

- but adds Hitless Switching and Phase Build-out functions

- Includes APC pin for Phase Build-out function (for absorption of the input phase change)

- Pin-selectable PLL divider ratios support forward and inverse FEC ratio translation

- Input reference and VCSO frequencies up to 700MHz (Specify VCSO frequency at time of order)

- Low phase jitter of 0.25 ps rms typical (12kHz to 20MHz or 50kHz to 80MHz)

- mercial and Industrial temperature grades

- Single 3.3V power supply

- Small 9 x...